# **COURSE GUIDE**

## **IFT236**

## ANALOG AND DIGITAL ELECTRONICS

Dr. Peter Dibal (Course Developer/Writer)-Computer Science, University of Maiduguri.

Prof Olayemi Mikail Olaniyi (Course Editor) **Course Team**

NOUN, Abuja

NATIONAL OPEN UNIVERSITY OF NIGERIA

© 2025 by NOUN Press National Open University of Nigeria Headquarters University Village Plot 91, Cadastral Zone Nnamdi Azikiwe Expressway Jabi, Abuja Lagos Office 14/16 Ahmadu Bello Way Victoria Island, Lagos e-mail: centralinfo@nou.edu.ng URL: www.nou.edu.ng All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher. First Printed: 2025 ISBN: 978-978-786-486-9

#### Introduction

Analogue and digital electronics are the central core of computing and computer systems. They provide the basis on which useful electronic systems are designed and built. It is against this backdrop that this course i.e. Analogue and Digital Electronics – a 3 credit unit course introduces the student to aspects of analogue and digital electronics with a view to enabling the student develop a basic competence in the subject area. Consequently, the student is introduced to the principle of operation and application of analogue and digital electronic components. The components that will come under focus include but not limited to amplifiers, filters, oscillators, analog-to-digital converters, transistors, logic gates, multiplexers, and decoders.

# **Course Competencies**

Upon undertaking this course, the student is expected to have a wide range knowledge of different types of analogue and digital electronics components, their distinguishing physical features and structures, and areas of applications. The student is also expected to have a good understanding of the behavior of the components under special circuit conditions, and also be able to identify early signs of component malfunction through measurements and analysis. Additionally, the student is expected to develop basic competence in the use of simulation and modeling tools like Simulink, Proteus VSM, PSpice, and Circuit Maker for the design and simulation of analogue, digital, and mixed electronic (analogue and digital) circuits, and rapid prototyping tools like Very High Speed Integrated Circuit Hardware Description Language (VHDL) for the rapid prototyping and Synthesis of digital electronic circuits.

# **Course Objectives**

The objectives of the course is revised and boldly divided into three sectionsobjectives for analog electronics, objectives for digital electronics, and objectives for modeling and simulations. The revision of the objectives and the addition of new ones are harmonized and presented as follows:

#### a. Course Objectives – Analog Electronics

- i. Identity different types of transistors, capacitors, and inductors from the perspective of their circuit symbols, and configurations.

- ii. Perform a detailed survey of the mathematical equations that govern the operation of important analog devices like transistors, capacitors, and inductors.

- iii. Perform in-circuit application and analysis of transistors, capacitors, and inductors

- iv. Identify different fundamental types of operational amplifier (op-amp) circuits which includes but not limited to voltage follower, inverting op-amp, non-inverting summing amplifier, differential amplifier, and integrator.

- v. Perform a detailed survey of the mathematical equations that govern the operation of different op-amp circuit configurations.

- vi. Perform in-circuit application and analysis of different op-amp circuits.

vii. Understand the design and analysis of DC power supply, voltage regulator circuits and analog-to-digital converters.

#### **b.** Course Objectives – Digital Electronics

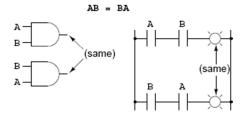

- i. Perform a detailed mathematical survey of Boolean algebra and its application digital circuits.

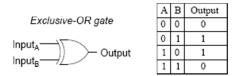

- Identify different types of logic gates like XOR, AND, OR, NOT, NAND from the perspective of circuit symbols and governing truth tables.

- iii. Understand Karnaugh maps and their applications in digital circuit minimization.

- iv. Identify different types of combinational circuits like decoders, multiplexers, encoders, adders, subtractors, multipliers, and demultiplexers from the perspective of circuit symbols and governing truth tables.

- v. Identify and understand the difference between types of sequential circuits i.e. asynchronous and synchronous sequential circuits.

- vi. Identify different types of sequential circuits like counters, flip-flops, and registers from the perspective of circuit symbols and governing truth tables.

## **Working Through this Course**

A thorough and excellent understanding of this course can be achieved through a systematic and methodic understanding of the contents that will move the reader from the basic to the advanced contents of the course. Further steps that will reinforce the understanding of the course is the study of the network of your organization or proposing one if there is none in existence and be committed to learning and implementing your knowledge.

The approximate duration of the course is 22 weeks under the assumption that the student gives undivided attention to the studies and commits to doing the exercises in the tutor-marked assignments that is expected to be submitted to the tutors

## **Study Units**

There are 12 study units in this course

#### Module 1

| Unit 1 | <b>Bipolar Junction Transistors</b> |

|--------|-------------------------------------|

| Unit 2 | Small Signal Amplifiers             |

| Unit 3 | Field Effect Transistor             |

#### Module 2

| Unit 1 | Operational amplifiers – Types, and Configurations             |

|--------|----------------------------------------------------------------|

| Unit 2 | Mathematical characterization of the functional behavior of op |

|        | amps.                                                          |

#### Module 3

| Unit 1 | Boolean algebra                                           |

|--------|-----------------------------------------------------------|

| Unit 2 | Logic gates – Types, circuits symbols, and truth tables   |

| Unit 3 | Karnaugh maps and logic circuit simplification            |

| Unit 4 | Combinational circuits – Arithmetic & Logic functions:    |

|        | Adders, Subtractors, Comparators                          |

| Unit 5 | Combinational circuits - Data transmission: Multiplexers, |

|        | Demultiplexers, Decoders, Encoders                        |

#### Module 4

| Unit 1   | Sequential circuits – Synchronous: flip-flops, register    | s, |

|----------|------------------------------------------------------------|----|

| counters |                                                            |    |

| Unit 2   | Sequential circuits – Asynchronous: Asynchronous: analysis | is |

|          | procedure, race conditions, stability considerations       |    |

## **References and Further Readings**

## **References for Analog Electronics**

- Gray, P. R., Hurst, P. J., Lewis, S. H. (2009). Analysis and Design of Analog Integrated Circuits. 5th Ed. *Wiley*. ISBN: 978-0470245996

- Dobkin, B., Williams, J. (2011). Analog Circuit Design: A Tutorial Guide to Applications and Solutions. *Newness*. ISBN: 978-0123851857

- Stephan, K. (2015). Analog and Mixed Signal Electronics. *Wiley*. ISBN: 978-1118782668

- Dimopoulus, H. G. (2011). Analog Electronic Filters. *Springer*. ISBN: 978-9400721890

- Pease, R. (2008). Analog Circuits: World Class Designs. *Newness*. ISBN: 978-0750686273

- Fiore, J. (2016). Operational Amplifiers & Linear Integrated Circuits: Theory and Applications. *Independently Published*. ISBN: 978-1796856897

- Huijsing, J. (2017). Operational Amplifiers: Theory and Design. 3rd Ed. *Springer*. ISBN: 978-3319281261

- Franco, S. (2016). Design with Operational Amplifiers and Analog Integrated Circuits. 4th Ed. *Mc Graw Hill India*. ISBN: 978-9352601943

#### **References for Digital Electronics**

Tokheim, R. L., Hoppe, P. E. (2021). Digital Electronics: Principles & Applications. 9th Ed. *Mc Graw Hill Education*. ISBN: 978-1260597868

- Kleitz, W. (2011). Digital Electronics: A Practical Approach with VHDL. 9th Ed. *Pearson*. 978-0132543033

- Ward, H. H. (2023). Mastering Digital Electronics. *Apress*. ISBN: 978-1484298800

- Maini, A. K. (2007). Digital Electronics: Principles, Devices, and Applications. *Wiley*. ISBN: 978-0470032145

- Anand, R. (2021). Digital Electronics: Digital Logic Design. *Khanna Book Publishing*

- Whitesitt, J. E. (2010). Boolean Algebra and Its Applications. *Dover Publications*. ISBN: 978-0486477671

- Gooroochurn, M. K. (2018). Introduction to Digital Logic and Boolean Algebra. *Independently Published*. ISBN: 978-1728793610

#### **Presentation Schedule**

The presentation schedule is characterized by important dates on which tutor marked assignments are to be completed and submitted. Adhering to the due dates is absolutely tangential for increasing a good understanding of the course and having time to address areas of weakness perceived from the submitted assignments.

The presentation schedule is included in the course materials.

#### Assessment

The assessment of this course is divided into two sections- tutor marked assignments, and written examination. In attempting the assignments, the candidate is kindly reminded that the knowledge gained during the course is absolutely tangential to a successful attempt. Consequently, candidates are strongly advised to take very seriously every aspect of the course as the assignments will make 30% of the grading of the course. Sequel to this, a written three-hour examination which makes 70% of the grading of the course will be administered. The examination shall be culled from the course materials and where appropriate, the tutor marked assignments.

#### **Tutor-Marked Assignment**

The tutor marked assignment section of the course shall be comprised of sixteen (16) assignments that shall be expected to be submitted for marking.

The total marks for the best four (4) assignments will be 30% of your total course mark.

Assignment questions for the units in this course are contained in the Assignment File. You should be able to complete your assignments from the information and materials contained in your set textbooks, reading and study units. However, you may wish to use other references to broaden your viewpoint and provide a deeper understanding of the subject.

When you have completed each assignment, send it together with form to your tutor. Make sure that each assignment reaches your tutor on or before the deadline given. If, however, you cannot complete your work on time, contact your tutor before the assignment is done to discuss the possibility of an extension.

## **Examination and Grading**

The final examination for the course shall carry 70% of the total marks available for the grading of this course. The examination will cover all aspects of the course; the candidate is therefore advised to revise all corrected assignments before the examination.

This course endows you with the status of a teacher and that of a learner. This means that you teach yourself and that you learn, as your learning capabilities would allow. It also means that you are in a better position to determine and to ascertain the what, the how, and the when of your course learning. No teacher imposes any method of leaning on you. The course units are similarly designed with the introduction following the table of contents, then a set of objectives and then the concepts and so on.

The objectives guide you as you go through the units to ascertain your knowledge of the required terms and expressions.

## **Course Marking Scheme**

This table shows the break down of marks allocation for the course.

| Assessment        | Marks                                                               |

|-------------------|---------------------------------------------------------------------|

| Assignment 1 – 4  | Best three out of four assignments to count for 30% of course marks |

| Final Examination | 70% of overall course marks                                         |

| Total             | 100% of course marks                                                |

Table 1: Course marking scheme

## **Course Overview**

After a review of the course overview, it was observed that there is the absence of a structured an systemic approach to the course that progressively enables the student develop higher understanding of each module as progress is made from one unit to another in the module. It was also observed the course overview does not equip the students with the ability to establish the

nexus between theoretical understanding of a unit in a module and the application of the unit in electronic designs via in-circuit applications. It is against this backdrop that the course overview has been reviewed an presented as follows.

| Unit  | Title of Work                                                                                     | Week(s)<br>Number | End of<br>Unit<br>Assessment |

|-------|---------------------------------------------------------------------------------------------------|-------------------|------------------------------|

|       | Course guide                                                                                      | 1                 |                              |

|       | Module 1                                                                                          |                   |                              |

| 1     | Bipolar Junction Transistors                                                                      | 1 - 2             |                              |

| 4     | Small Signal Amplifiers                                                                           | 3                 | Assignment 1                 |

| 5     | Field Effect Transistors                                                                          | 4                 | Assignment 2                 |

|       | Module 2                                                                                          |                   |                              |

| 1     | Operational amplifiers – Types, and Configurations                                                | 5                 | Assignment 3                 |

| 2     | Mathematical characterization of the functional behavior of op amps.                              | 6                 | Assignment 4                 |

|       | Module 3                                                                                          | •                 |                              |

| 1     | Boolean algebra                                                                                   | 8                 | Assignment 6                 |

| 2     | Logic gates – Types, circuits symbols, and truth tables                                           | 9                 | Assignment 7                 |

| 3     | Karnaugh maps and logic circuit simplification                                                    |                   |                              |

| 4     | Combinational circuits – Arithmetic & Logic functions:<br>Adders, Subtractors, Comparators        | 10 - 11           | Assignment 8                 |

| 5     | Combinational circuits – Data transmission: Multiplexers, Demultiplexers, Decoders, Encoders      | 12 - 13           | Assignment 9                 |

|       | Module 4                                                                                          |                   |                              |

| 1     | Sequential circuits – Synchronous: flip-flops, registers, counters                                | 14 - 15           | Assignment 10                |

| 2     | Sequential circuits – Asynchronous: analysis procedure, race conditions, stability considerations | 16 - 17           | Assignment 11                |

| Revis | Revision                                                                                          |                   |                              |

| Exam  | ination                                                                                           | 19                |                              |

| Total | Total 22 weeks                                                                                    |                   |                              |

# How to get the Most from the Course

In distance learning the study units replace the university lecturer. This is one of the great advantages of distance learning; you can read and work through specially designed study materials at your own pace, and at a time and place that suit you best. Think of it as reading the lecture instead of listening to a lecturer. In the same way that a lecturer might set you some reading to do, the study units tell you when to read your set books or other material. Just as a lecturer might give you an in-class exercise, your study units provide exercises for you to do at appropriate points.

Each of the study units follows a common format. The first item is an introduction to the subject matter of the unit and how a particular unit is integrated with the other units and the course as a whole. Next is a set of learning objectives. These objectives enable you know what you should be able to do by the time you have completed the unit. You should use these

objectives to guide your study. When you have finished the units you must go back and check whether you have achieved the objectives. If you make a habit of doing this you will significantly improve your chances of passing the course. Remember that your tutor's job is to assist you. When you need help, don't hesitate to call and ask your tutor to provide it.

- i. Read this Course Guide thoroughly.

- ii. Organize a study schedule. Refer to the 'Course Overview' for more details. Note the time you are expected to spend on each unit and how the assignments relate to the units. Whatever method you chose to use, you should decide on it and write in your own dates for working on each unit.

- iii. Once you have created your own study schedule, do everything you can to stick to it. The major reason that students fail is that they lag behind in their course work.

- iv. Turn to Unit 1 and read the introduction and the objectives for the unit.

- v. Assemble the study materials. Information about what you need for a unit is given in the 'Overview' at the beginning of each unit. You will almost always need both the study unit you are working on and one of your set of books on your desk at the same time.

- vi. Work through the unit. The content of the unit itself has been arranged to provide a sequence for you to follow. As you work through the unit you will be instructed to read sections from your set books or other articles. Use the unit to guide your reading

- vii. Review the objectives for each study unit to confirm that you have achieved them. If you feel unsure about any of the objectives, review the study material or consult your tutor.

- viii. When you are confident that you have achieved a unit's objectives, you can then start on the next unit. Proceed unit by unit through the course and try to pace your study so that you keep yourself on schedule.

- ix. When you have submitted an assignment to your tutor for marking, do not wait for its return before starting on the next unit. Keep to your schedule. When the assignment is returned, pay particular attention to your tutor's comments, both on the tutor-marked assignment form and also written on the assignment. Consult your tutor as soon as possible if you have any questions or problems.

- x. After completing the last unit, review the course and prepare yourself for the final examination. Check that you have achieved the unit objectives (listed at the beginning of each unit) and the course objectives (listed in this Course Guide).

#### **Facilitation**

There are 12 hours of tutorials provided in support of this course. You will be notified of the dates, times and location of these tutorials, together with the name and phone number of your tutor, as soon as you are allocated a tutorial group.

Your tutor will mark and comment on your assignments, keep a close watch on your progress and on any difficulties you might encounter and provide

assistance to you during the course. You must mail or submit your tutor-marked assignments to your tutor well before the due date (at least two working days are required). They will be marked by your tutor and returned to you as soon as possible.

Do not hesitate to contact your tutor by telephone, or e-mail if you need help. The following might be circumstances in which you would find help necessary. Contact your tutor if:

- you do not understand any part of the study units or the assigned readings,

- you have difficulty with the self-tests or exercises,

from participating in discussions actively.

• you have a question or problem with an assignment, with your tutor's comments on an assignment or with the grading of an assignment.

You should try your best to attend the tutorials. This is the only chance to have face-to-face contact with your tutor and to ask questions which are answered instantly. You can raise any problem encountered in the course of your study. To gain the maximum benefit from course tutorials, prepare a question list before attending them. You will learn a lot

## Ice Breaker

Students are to write what they know about analogue and digital electronics, and what they also expect from the course.

# MAIN COURSE

# **CONTENTS**

| Module 1 |                                                    | 1  |

|----------|----------------------------------------------------|----|

| Unit 1   | Bipolar Junction Transistors                       | 1  |

| Unit 2   | Small Signal Amplifiers                            | 20 |

| Unit 3   | Field Effect Transistor                            | 33 |

| Module 2 |                                                    | 42 |

| Unit 1   | Operational amplifiers – Types, and Configurations | 42 |

| Unit 2   | Mathematical characterization of the functional    |    |

|          | behavior of op amps                                | 56 |

| Module 3 |                                                    | 65 |

| Unit 1   | Boolean algebra                                    | 65 |

| Unit 2   | Logic gates – Types, circuits symbols,             |    |

|          | and truth tables                                   | 7  |

| Unit 3   | Karnaugh maps and logic circuit simplification     | 80 |

| Unit 4   | Combinational circuits – Arithmetic &              |    |

|          | Logic functions: Adders, Subtractors, Comparators  | 88 |

| Unit 5   | Combinational circuits – Data transmission:        |    |

|          | Multiplexers, Demultiplexers, Decoders, Encoders   | 90 |

| Module 4 |                                                    | 10 |

| Unit 1   | Sequential circuits – Synchronous: flip-flops,     |    |

|          | registers, counters                                | 10 |

| Unit 2   | Sequential circuits – Asynchronous:                |    |

|          | Asynchronous: analysis procedure, race conditions, |    |

|          | stability considerations                           | 11 |

|          | •                                                  |    |

#### **MODULE 1**

| Unit 1 | Bipolar Junction Transistors |

|--------|------------------------------|

| Unit 2 | Small Signal Amplifiers      |

| Unit 3 | Field Effect Transistors     |

## UNIT 1 BIPOLAR JUNCTION TRANSISTORS

#### **CONTENTS**

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Bipolar Junction Transistor

- 3.2 Bipolar Junction Transistor Configurations

- 3.3 Load Lines

- 3.4 Bipolar Junction Transistor Biasing

- 3.5 Common Emitter Biasing

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Readings

#### 1.0 INTRODUCTION

A transistor is a three-terminal semiconductor device that can be used for amplification and switching. Amplification consists of magnifying a signal by transferring energy to it from an external source; whereas a transistor switch is a device for controlling a relatively large current between or voltage across two terminals by means of a small control current or voltage applied at a third terminal. There are two major families of transistors are bipolar junction transistors, or BJTs; and field-effect transistors, or FETs. As will be shown, the BJT acts essentially as a current-controlled device, while the FET behaves as a voltage-controlled device.

#### 2.0 OBJECTIVES

At the end of this unit, students should be able to:

- be able to IDENTIFY basic transistor amplifier topologies

- be able to ANALYZE basic amplifier topologies for gains and resistances

- be able to DISCUSS the relative properties of various amplifier topologies

• be able to DESIGN basic amplifiers to meet or exceed stated specifications.

#### 3.0 MAIN CONTENT

The Bipolar Junction Transistor (BJT)

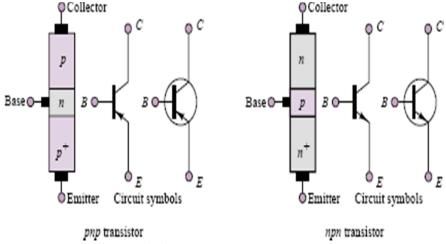

The pn junction forms the basis of a large number of semiconductor devices. A BJT is formed by joining three sections of semiconductor material, each with a different doping concentration. The three sections can be either a thin nregion sandwiched between p+ and p layers, or a p region between n and n+ layers, where the superscript "plus" indicates more heavily doped material. The resulting BJTs are called pnp and npn transistors, respectively:

The figure 1.1 below shows the block diagrams and circuit symbols of both the npn ad the pnp transistors.

Figure 1.1 transistor symbols

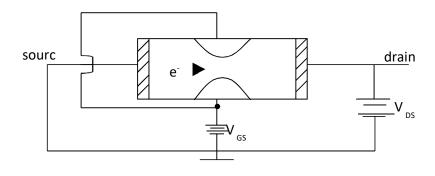

Figure 1.2 electron flows in transistors

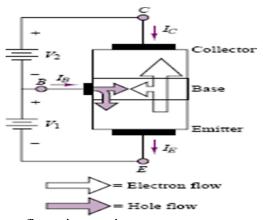

The operation of the npn BJT can be explained by considering the transistor as consisting of two back-to-back pn junctions. The baseemitter (BE) junction acts very much like a diode when it is forwardbiased; thus, the corresponding flow of hole and electron currents from base to emitter when the collector is open and the BE junction is forward-biased, is shown in figure 1.2. Note that the electron current has been shown larger than the hole current, because of the heavier doping of the n side of the junction. Some of the electron-hole pairs in the base will recombine; the remaining charge carriers will give rise to a net flow of current from base to emitter. It is also important to observe that the base is much narrower than the emitter section of the transistor.

The flow of electrons in the transistor is represented by the equation below.

$$IE = IB + IC 1$$

Since the transistor is biased in the active region a small base current controls the much larger collector current.

where

$$IC = \beta IB$$

where  $\beta$  is a current amplification factor dependent on the physical properties of the transistor. Typical values of  $\beta$  range from 20 to 200. The operation of a pnp transistor is completely similar to that of the npn device, with the roles of the charge carriers (and therefore the signs of the currents) reversed.

| IE 🗆                        |

|-----------------------------|

| IE 🗆                        |

| $\Box$                      |

| (1 □                        |

| □ I B 3                     |

| □ )IB 4                     |

| from the equation (4) above |

$$I_{B} = \frac{I_{E}}{(1+\beta)}$$

$$I_{C} = \left(\frac{\beta}{1+\beta}\right)I_{E}$$

...

6

Equation 6 can be written as

Thus

$$\alpha = \left(\frac{\beta}{1+\beta}\right)$$

where  $\alpha =$  common base gain IC  $\square$

$\Box$  IE

**Bipolar Junction Transistor Configurations**

Transistors can be configured in three different modes with one pair of terminals for the input and another pair for the output. These configurations are:

Common emitter

Common collector

Common base.

Common Emitter

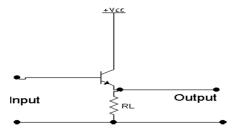

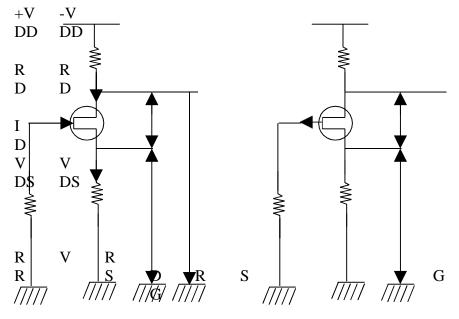

In the common emitter configuration, the input terminal is the base while the output terminal is the collector and the emitter is common to both the input and the output as shown in figure 1.3 below.

Figure 1.3 Common Emitter configurations

α

The current gain for this configuration is given by

output \_ current □ IC

input \_ current

IB

#### Common Collector

In the common collector configuration, the input terminal is the base while the output terminal is the emitter and the collector is common to both the input and the output as shown in figure 3.4 below.

Figure 1.4 Common collector configurations

ΙE

The current gain for this configuration is given by  $\frac{1}{I}$

В

Common Base

In the common base configuration, the input terminal is the emitter while the output terminal is the collector and the base is common to both the input and the output as shown in figure 1.5 below

Figure 1.5 common base configuration

IC The current gain for this configuration is given by  $\overline{I}$  E

The gain for the CB configuration is always less than 1, so the CB configuration is not used for current amplification .The CC and CE configurations both have a high gain but the input impedance of the CE configuration is higher than that of the CC. This makes the CE configuration the preferred choice for amplifiers in circuit design.

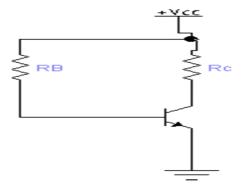

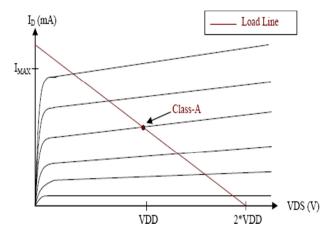

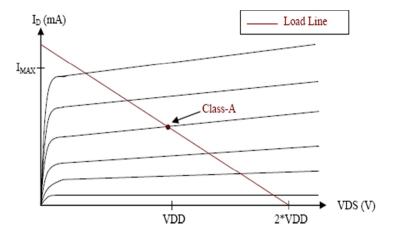

#### **Loads Lines**

The load line is a line drawn based on the DC operating characteristics of the circuit. It enables the visualization of the transistor characteristics. It is determined by using the DC equations of the circuit. The Ic (max) and Vce (max) are used to determine the end points of the line, these points are then joined together and superimposed on the transistor characteristics.

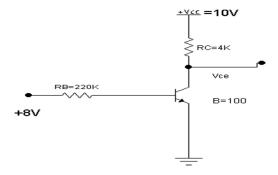

Figure 1.6 Amplifier circuit

From the circuit 1.6, the analysis is done below From the output equation

Vcc □ ICRC □ VCE

The load line is determined by identifying the two endpoints of the line. The are determined by assuming VCE = 0 and finding Ic, and the V subscribe is determined by assuming Ic = 0.

From the output equation, with Ic = 0, Vcc = VCEWith VCE = 0 Vcc = IcRc $Ic(max) = \underline{Vcc}$ Rc

The load line is sketched in the figure 1.7 below

Figure 1.7 load line

The curves are generated at different base currents. The Q point (operating Point) is the intersection of the Ic and the Vce on the load line for any particular base current.

From the graphs, as Ic rises from 0, the mode of operation of the transistor changes from cutoff to active and when the Ic gets to the maximum, the transistor gets to the saturation region of operation.

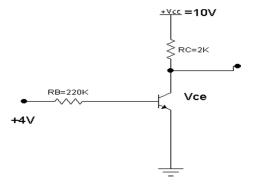

## Example 1

Given the circuit below, determine the load line.

From the output equation

$Vcc \square ICRC \square VCE$

With Vce = 0

2.5mA

With Ic = 0

Vce = 10V

**Bipolar Junction Transistor Biasing**

The transistor can serve either as a switch or an amplifier. The mode of operation of each transistor is determined by the bias condition in which it operates.

Biasing can be defined as the setting up of the DC voltages and current in an electronic circuit.

From the output characteristics, the transistor has 3 regions of operation.

Saturation region Active region Cutoff region

Figure 1.8 Q-point

The Q point or dc operating point is that point on the load line where the Icq and Vceq intercept on the load line. The transistor when operating as a switch is biased in the saturation or cutoff region but for the transistor to be used as an amplifier it is biased in the active region. With transistor in the forward active region the voltage across the B-E junction is V subscribe (on) is 0.7V for silicon transistors and 0.4V for germanium transistors.

The determination of the q point is through the process of biasing. Example 2

Calculate the base, collector and emitter currents for the circuit shown below.

$$\beta = 200$$

From the output equation Vcc = IcRc + VCEFrom the input equation

VBB= IBRB + VBE

I = VBB

$$\square$$

VBE  $\square$

RB

4  $\square$  0.7  $\square$  15  $\square$  A

220K

Ic = βIB = (200)(15μA) = 3mA

IE = (1+β).

IB = (200+1) (15μA) = 3.02mA

VCE = Vcc - IcRc = 10 - (3mA)(2K) = 4V

## Types Common Emitter Biasing

There are different types of bias circuit with each having its advantages and disadvantages.

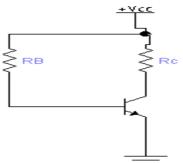

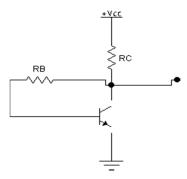

## 1. Base Bias

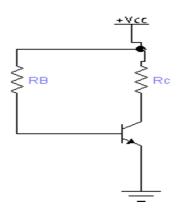

This is the simplest type and is also known as fixed bias. The quiescent base current is established by a single base resistor as shown in figure 1.9 below.

Figure 1.9 base bias

Biasing of this circuit will involve the selection of appropriate values for the base resistance and collector resistance.

| Analysis                   |     |

|----------------------------|-----|

| Input equation             |     |

| Vcc □ IBRB □ VBE<br>IBRB □ | (1) |

| IBQ □                      |     |

| VCC □ VBE                  |  |

|----------------------------|--|

| VCC □ VBE<br>RB            |  |

| (2)                        |  |

| (3) RB □ VCC □ VBE IBQ (4) |  |

This equation yields the Quiescent base current IBQ

From the circuit, the output equation is derived below

Vcc □

$ICRC \ \Box \ VCE$

(5)

ICQRC □

$VCC \square VCE$  (6)

$ICQ \square$

RC \_\_\_\_

VCC □ VCE RC

VCC □ VCE

ICQ \_\_\_\_\_

(7)

(8)

## Example 3

Given the circuit below, design the amplifier for the following specifications:

$$VCC = 12V, \ \beta = 100, \ V\overline{b}e = 0.7, \qquad Icq = 1mA \qquad Vceq = 6V$$

Solution

| VCC $\square$                                                   |

|-----------------------------------------------------------------|

| IBRB □ IBRB □ IBRB □ VBE                                        |

| VCC □ VBE □ II .3V                                              |

| 12 □ 0.7  From the output equation Vcc □ IcRc □                 |

| IcRc $\square$ Vce Vcc $\square$ Vce $\square$                  |

| 12   6 12   6 Ic   ———————————————————————————————————          |

| The base resistance is determined from the input equation to be |

| IBQRB □ VCC □ Vbe(on)  12 □ 0.7  RB □ 10□ A  □ 1 13M□           |

$$Vcc = IcRc + Vce$$

$Ic = 0$ ,

$$Vce = Vcc = 12V$$

$$Vce = 0$$

$$Ic = \frac{Vcc}{Rc} = \frac{12}{6K} = 2mA$$

The load line is determined to be

From the various formulas used above, the Icq is dependent to a large extent on the  $\beta$ . The beta ( $\beta$ ) varies with temperature so any circuit built with too much dependence on  $\beta$  will be very unstable.

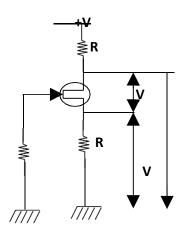

## Base Bias with Collector Feedback

The base is connected to the collector as shown in the circuit in figure 1.10 below

Figure 1.10 Base bias with collector feedback

Output equation

VCC □ (IC □ I B )RC □ VCE 1

The collector current and the base currents flow through the collector resistor

But IC >> IB

$$IC(sat) = \underline{Vcc}$$

Rc

Since there is no emitter resistor the out put equation becomes

VCC □

(IC □

I B )RC □ VC

VC □ Vcc □

(IC □

I B )RC

Since Vc also forms part of the input equation, the input equation becomes:

$$V_c = I_s R_s + V_{ss}$$

$$Vcc - (I_C + I_B)R_C = I_BR_B + V_{BE}$$

Since Ic>> IB

$$Vcc - IcRc = I_sR_s + V_{sz}$$

But

$$I_B = \frac{Ic}{\beta}$$

$$\frac{IcR_B}{\$} + V_{BE} = Vcc - I_CR_C$$

The collector current can be derived from the expression below.

Vcc □ VBE Ic □ \_\_\_\_\_\_ RB □ Rc □ □ I E

From the expression for collector current, the effect of the transistor gain on the collector current is reduced leading to better system stability.

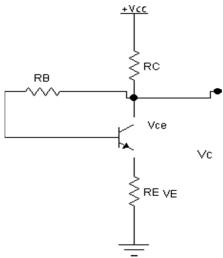

Base Bias with Collector and Emitter Feedback

Figure 1.11 Base Bias with collector and emitter feedback

From the output equation:

$$V_{cc} = (I_c + I_E)R_c + V_{cE} + I_E R_E$$

$$I_C >> I_B \text{ and } I_C = I_E$$

$$V_{cc} = I_c R_c + V_{cE} + I_C R_E = V_{cE} + I_C (R_c + R_E)$$

$$I_C = \frac{V_{cc} - V_{cE}}{(R_E + R_E)}$$

At saturation (VCE =0)

$$\begin{array}{c|c}

I & \Box & VCC \\

\hline

C & (R \Box R) \\

C &

\end{array}$$

The actual value of Ic is derived using the input equation since in most cases the VCE is unknown

From the input equation

$$V_{CC} = I_C R_C + V_{BE} + I_B R_B + I_C R_E$$

$$V_{CC} - V_{BE} = I_C(R_C + R_E) + I_B R_B$$

But

$$I_B = \frac{I_C}{\beta}$$

$$V_{CC} - V_{BE} = I_C(R_C + R_E) + \frac{R_B}{\beta}$$

$$I_C = \frac{V_{CC} - V_{BE}}{(R_E + R_C + \frac{R_B}{\beta})}$$

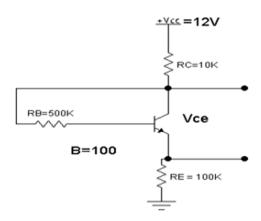

# Example 4

Determine the Ic(sat), VCE and Vc. In the circuit below. Neglect VBE

From the output equation:

$$V_{cc} = (I_c + I_g)R_c + V_{ce} + I_E R_E$$

$I_C >> I_B$  and  $I_C = I_E$

$$V_{cc} = I_c R_c + V_{cz} + I_c R_{\overline{c}} = V_{cz} + I_c (R_c + R_{\overline{c}})$$

$$I_C = \frac{V_{CC} - V_{CE}}{(R_E + R_C)}$$

At saturation (VCE =0)

$$I_c(sat) = \frac{12}{(100K + 10K)} = 0.11mA$$

$$V_C = V_{CE} + V_E$$

$$V_{c\varepsilon} = V_{cc} - I_c (R_c + R_{\varepsilon})$$

$$V_E = I_E R_E$$

To determine IC we use the input equation

VCC

$IC RC \square VBE \square$

I B RB □

I E RE

Since IC = IE

VCC

$IC RC \square VBE \square$

I B RB □

IC RE

$VCC \square VBE \square$

IC (RC □

RE )  $\square$

I B RB

But

VCC

$IB \square$

**VBE**

$0.1\text{mA}(110\text{K}) \square 1\text{V}$

VC = VCE + VE = 1 + ICRE = 1 + 0.1 mA(100K) = 11VVoltage Divider Bias

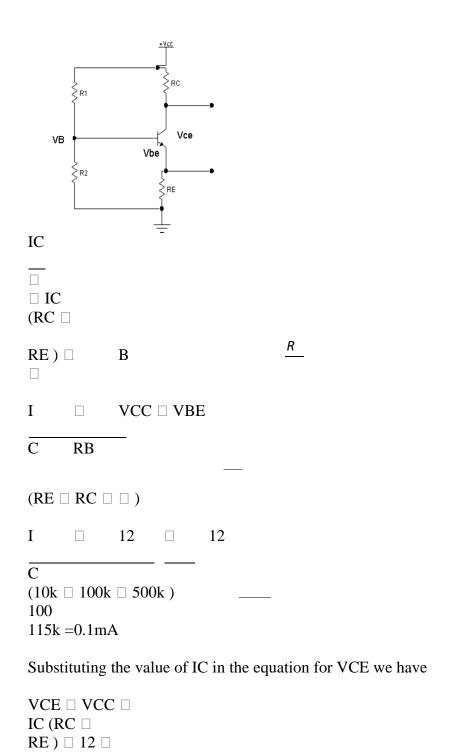

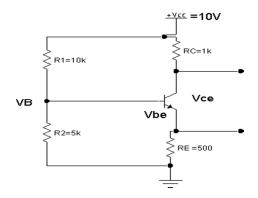

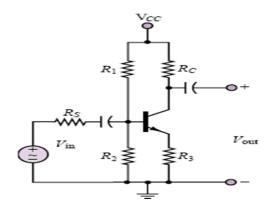

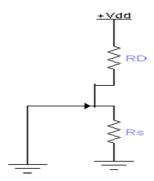

From the circuit diagram in figure 1.12, the voltage divider bias is analyzed below as follows.

Figure 1.12 Voltage divider bias

From the potential (voltage) divider equation  $VB \sqcap$ Vcc \* R2  $\overline{R1} \square R2$ VB = Vbe + VEVE = VB - Vbebut VB >>Vbe IE = $VE \square$ **RE** VB □ Vbe □ VB RE RE From the output equation VCC IC RC □ VCE □ I E RE VC = VCE + VEVCE □ VCC □ IC (RE □ RC) With VCE = 0 in the output equation, Ic is determined as Vcc IC(sat) = RC

The base voltage is set by the resistors R1 and R2 thus the effect of the transistor forward gain is reduced .The D.C bias is independent of  $\beta$ .

## 4.0 CONCLUSION

In this unit you have been introduced to the transistor amplifier and the different types of biasing arrangements and transistor configurations.

## 5.0 SUMMARY

In this unit we have been able to extend knowledge of the theory and applications of transistors and transistor amplifier design.

## 6.0 TUTOR-MARKED ASSIGNMENT

Determine the VCE and IC in the circuit diagram shown below. Vbe = 0.7

2. Given the circuit below, design the amplifier for the following specifications:

$$VCC = 12V, \beta = 100, Vbe = 0.7, Icq = 1mA Vceq = 6V$$

# 7.0 REFERENCES/FURTHER READING

Fitchen F.C; (1972). Transistor Circuit Analysis and Design. Second Edition Van Nostrand Reinhold Publishers.

Maddock R.J and Calcutt D.M (1994). Electronics: a Course for Engineers Second Edition. Longman Publishers.

Neamen D.A (1996). Electronics Circuit Analysis and Design.

McGraw-Hill Publishers.

#### UNIT 2 SMALL SIGNAL AMPLIFIERS

#### CONTENTS

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Transistor Hybrid Parameters

- 3.2 Analysis of a Single Stage Transistor Amplifier Small Signal

- 3.3 Operation

- 3.4 Input Impedance

- 3.5 Output Impedance

- 3.6 Voltage Gain

- 3.7 Effect of Bypass Capacitor on Common Emitter Amplifier

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/ Further Readings

#### 1.0 INTRODUCTION

Electronic amplifying devices such as BJT and FET have three terminals (E,B,C and S, G,D). In a basic amplifying circuit, one of the terminals is made common while the other two serve as input and output ports. Small-signal models for the BJT take advantage of the relative linearity of the base and collector curves in the vicinity of an operating point. These linear circuit models work very effectively, providing that the transistor voltages and currents remain within some region around the operating point. This condition is usually satisfied in small-signal amplifiers used to magnify low-level signals (e.g., sensor signals). For the purpose of our discussion, we use the hybrid-parameter (hparameter) small-signal model of the BJT, to be discussed presently. Note that a small-signal model assumes that the DC bias point (Q-point) of the transistor has been established. The following convention will be used: each voltage and current is assumed to be the superposition of a DC component (the quiescent voltage or current) and a small-signal AC component. The former is denoted by an uppercase letter and the latter by an uppercase letter preceded by the symbol  $\Delta$ . Thus,

$$iB = IBQ + \Delta IB iC = ICQ + \Delta IC$$

$vCE = VCEQ + \Delta VCE$

#### 2.0 OBJECTIVES

At the end of this unit, student should be able to:

- be able to IDENTIFY the transistor hybrid parameters

- be able to ANALYZE amplifier topologies for gains and impedances

- be able to DISCUSS the relative properties of various amplifier configurations

- be able to DESIGN basic amplifiers to meet or exceed stated specifications.

## 3.0 MAIN CONTENT

Transistor Hybrid parameters

The Hybrid parameters are specifications used in the analysis of transistor amplifiers there are four h parameters and these are:

The parameter hie which is approximately equal to the ratio  $\Delta$  VBE/ $\Delta$ IB. Physically, this parameter represents the forward resistance of the BE junction.

The parameter hre which is representative of the fact that the IB- VBE curve is slightly dependent on the actual value of the collector- emitter voltage, VCE. However, this effect is virtually negligible in any applications of interest to us. Thus, we shall assume that hre  $\approx 0$ . A typical value of hre for VCE  $\geq 1$  V is around 10-2.

The parameter hf e is the current ratio  $\Delta$  IC / $\Delta$ IB. This parameter represents the current gain of the transistor and is approximately equivalent to the parameter  $\beta$  introduced earlier. For the purpose of our discussion,  $\beta$  and hf e will be interchangeable, although they are not exactly identical.

The parameter hoe may be calculated as hoe =  $\Delta$ IC/  $\Delta$  VCE From the collector characteristic curves. This parameter is a physical indication of the fact that the IC-VCE curves in the linear active region are not exactly flat; hoe represents the upward slope of these curves and therefore has units of conductance (S). Typical values of hoe are around 10-5 S. this parameter is often assumed to be negligible.

$$h_{ie} = \frac{\partial v_{BE}}{\partial i_B} \Big|_{I_{BO}}$$

(\O)

$$h_{oe} = \frac{\partial i_C}{\partial v_{CE}} \Big|_{V_{CEO}}$$

(S)

$$h_{fe} = \frac{\partial i_C}{\partial i_B} \Big|_{I_{BO}} \qquad \left(\frac{A}{A}\right)$$

$$h_{re} = \frac{\partial v_{BE}}{\partial v_{CE}} \Big|_{V_{CEO}} \qquad \left(\frac{\mathbf{V}}{\mathbf{V}}\right)$$

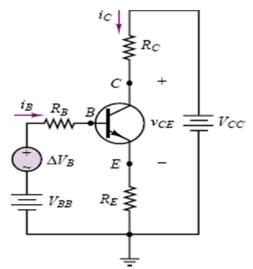

Analysis of a Single Stage Transistor Amplifier Small Signal Operation

In order to fully analyze a transistor amplifier, the analysis is broken into AC and DC analysis. In the DC analysis all capacitors are regarded as open circuits, while for the AC analysis, the capacitors are regarded as short circuits and the DC source is replaced by a ground.

The purpose of the analysis is to determine the different specifications of the circuit. These specifications include the input impedance, output impedance and the circuit gain.

## Example 1

Given the circuit below, determine the Q point voltage and current values and AC open-loop voltage gain of the amplifier of Figure 2.1; the amplifier employs a 2N5088 npn transistor.  $\beta$ =350

Figure 2.1

**Analysis**

Q-point calculation

We first write the collector circuit equation by applying KVL:

$$VCC = VCE + RCIC + REIE = VCE + RCIC + RE(IB + IC)$$

$$\approx$$

VCE + (RC + RE)IC

where the emitter current has been approximately set equal to the collector current since the current gain is large and IC >> IB.

Next, we write the base circuit equation, also via KVL:

$$VBB = RBIB + VBE + REIE = (RB + (\beta + 1)RE)IB + Vbe$$

The above equation can be solved numerically (with hf  $e = \beta$ ) to obtain:

$$I_B = \frac{V_{BB} - V_{BE}}{R_B + (\beta + 1)R_E} = \frac{6 - 0.6}{100 \times 10^3 + 351 \times 100} = 40 \mu A$$

Then,

$$IC = \beta IB = 350 \text{ X } 40 \text{ x } 10-6 = 14 \text{ mA}$$

and

$$VCE = VCC - (RC + RE)IC = 12 - 600 \times 40 \times 10 - 3 = 3.6 \text{ V}$$

Thus, the Q point for the amplifier is:

$$IBQ = 40 \mu A$$

,  $ICQ = 14 \text{ mA}$  and  $VCEQ = 3.6 \text{ V}$

Confirming that the transistor is indeed in the active region.

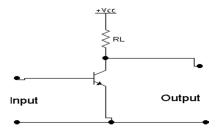

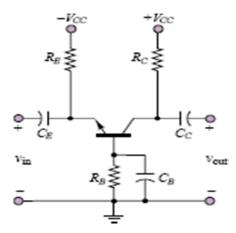

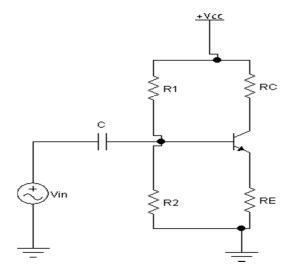

From previous discussion, it has been verified that the common emitter configuration is the best for signal amplification. We shall be looking at the single stage common emitter amplifier.

Any amplifier circuit has the following parts:

The Bias Circuit

The Load Circuit

The Coupling Circuit

The bias circuit has been discussed so we focus on the other component parts.

Fig 2.2: CE amplifier circuit

From the diagram above, the following are the responsibility of the different components.

C = Coupling capacitor. it prevents dc signals in the source from upsetting the amplifier's Q point values.

R1 and R2 = potential divider bias resistors

RC = load/collector resistor

RE = Emitter resistor

Given a common emitter amplifier circuit, to analyze such a circuit we need to consider its DC and AC characteristics.

## Example 2

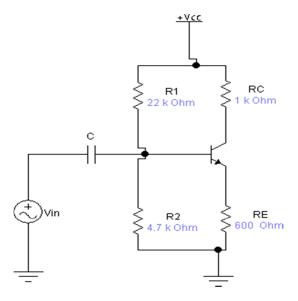

Given the circuit with the following parameters below, ( $\beta$ dc =150 and  $\beta$ ac = 160)

where  $\beta dc$  =DC gain and  $\beta ac$  = AC gain. Determine the circuit specifications given the following component parameters. RE =  $600\Omega$  Rc =  $1k\Omega$  R1 =  $22k\Omega$  R2=  $4.7k\Omega$

Fig 2.3: CE amplifier circuit

In order to understand the operation of the circuit given above, we will have to perform both the DC and AC analysis.

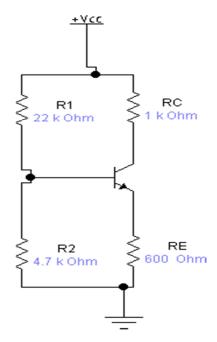

## DC Analysis

Before the DC analysis is performed, all coupling capacitors are regarded as open circuit. This will yield the following representation of the circuit above.

Fig 2.4:

| From Ohms Law,                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rin □<br>Vin Iin                                                                                                                                                                                                                                                            |

| $\label{eq:Vin} \begin{tabular}{ll} Vin = &Vbe + IERE \ . \ Vbe = 0.7 \ for \ silicon \ transistor \ which \ is \ the \ most \ widely \ used \ type. \ IERE >> Vbe \end{tabular}$                                                                                           |

| Vin = IERE                                                                                                                                                                                                                                                                  |

| Rin □I E RE                                                                                                                                                                                                                                                                 |

| $\begin{tabular}{ll} \hline Iin \\ Vin & \Box \\ IinRin & \Box \\ IE RE \\ but IE & \Box Ic = \beta Ib \ . The base current Ib is the input current and RIN is the resistance at the base so, Iin = Ib and RIN = RB \\ Vin & \Box \\ & \Box \ IbRE = IbRB \\ \end{tabular}$ |

| $RB \ \Box \ \Box$ IbRE Ib canceling Ib from both the numerator and denominator we have the DC input resistance RB to be, RB $\ \Box \ \Box$ RE                                                                                                                             |

| Inserting the values of the components, the Dc input resistance of the circuit is given by                                                                                                                                                                                  |

| RIN = RB $\square$ dcRE =150 x 600 = 90K $\Omega$                                                                                                                                                                                                                           |

| Note: If RB is more than 10 times R2 then the voltage divider rules is used VB $\square$ $\square$ R2 $\square$ Vcc $\square$ $\square$                                                                                                                                     |

| 4.7k    x12     2.11V   R1     R2       22k     4.7k     VE = VB - Vbe = 2.11 - 0.7 = 1.41V IE = VE     RE                                                                                                                                                                  |

mA

Since Ic =IE

$$VC = Vcc$$

-  $IcRC = 12 - 2.4 = 9.6V VCE = VC - VE = 9.6 - 1.41 = 8.19V$

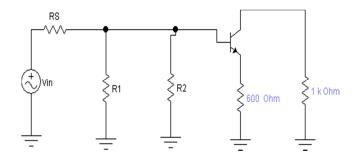

## AC Analysis

For the ac analysis, the circuit is redrawn with the following assumptions:

All capacitors are short circuit

DC sources are replaced by ground

This circuit is further reduced to the circuit shown below

Rin (base) is the resistance at the base of the transistor and it is derived with the ac emitter resistance added in series to the RE.

Rin (base) =

$$\beta$$

ac(re + RE)

The ac emitter resistance is given by

$$re = \frac{25mV}{IE}$$

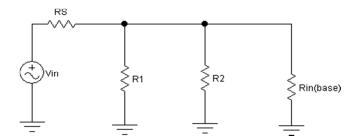

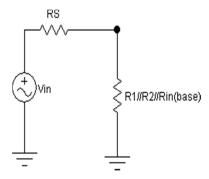

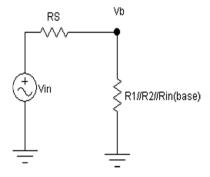

## 3.3 Input Impedance

The total input impedance of the circuit is the parallel combination of R1,R2 and Rin(base). Thus the circuit is reduced to the following:

Input Impedance = R1/R2/Rin(base).

From the component values of the circuit assuming a source impedance of  $300\Omega$ , the input impedance is computed to be

Rin(base) =

$$160(re + 600)$$

But re  $\square 25mV$

IE  $25mV$

$\overline{mA=10.4\Omega}$

IE is the DC emitter current computed to be 2.4mA. Rin (base) = 160 (10.4 + 600) Rin(base) =  $160(610.4) = 97664 \Omega$

The voltage at the base of the transistor (Vb) is determined below

If RS << Rin(input impedance) then Vb = Vin. If not then the voltage divider equation is used as shown below.

$$Vb = \left(\frac{Rin}{RS + Rin}\right)Vin$$

Compute the input impedance and the voltage at the base of the transistor

## Output Impedance

The output resistance looking at the collector is approximately equal to RC. In situations where a load is connected in parallel with the RC, the output resistance will be equal to the parallel combination of both the Rc and the load resistance. Thus a load (RL) connected to the output affects the gain.

The voltage gain is the ratio between the output voltage and the input voltage.

| AV $\square$ $\square$ Output _ voltage $\square$ |  |

|---------------------------------------------------|--|

|                                                   |  |

|                                                   |  |

| VC □                                              |  |

|                                                   |  |

|                                                   |  |

| Input _ voltage □                                 |  |

| IcRC                                              |  |

| Vb IE(re □                                        |  |

| IERC                                              |  |

| RE)                                               |  |

| IE(re □                                           |  |

| $AV \square$                                      |  |

| RE) RC                                            |  |

| (re $\square$ RE)                                 |  |

| RE)                                               |  |

This is the voltage gain from the base to the collector of the transistor.

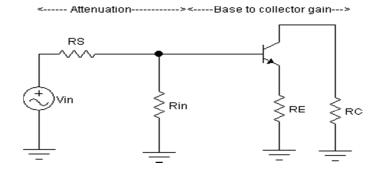

The total circuit gain is made up of the attenuation due to the source resistance and the base to collector gain as shown below.

$$Vb = \left(\frac{Rin}{RS + Rin}\right)Vin$$

$$AV^{I} = \frac{RC}{(re + RE)} \left( \frac{Vb}{Vin} \right)$$

Effects of Emitter Bypass Capacitor on the CE Amplifier

When a capacitor is connected across the emitter resistor it bypasses the RE as the capacitor acts as a sort circuit for the AC signals. Thus the Ac voltage gain becomes

AV □ RC

\_\_\_\_

(re)

RE is neglected and the gain increases.

This increase in gain however leads to a reduction in gain stability because the re ( ac emitter resistance varies with temperature)

## 4.0 CONCLUSION

In this unit you have been introduced to the small signal operation of the BJT amplifier and the transistor hybrid parameters.

## 5.0 SUMMARY

In this unit we have been able to extend knowledge of the theory and applications of transistors and small signal transistor amplifier design.

## 6.0 TUTOR-MARKED ASSIGNMENT

Determine the Q point of the amplifier shown below. Vbe = 0.7 V;  $\beta$  = 100; VCC = 15

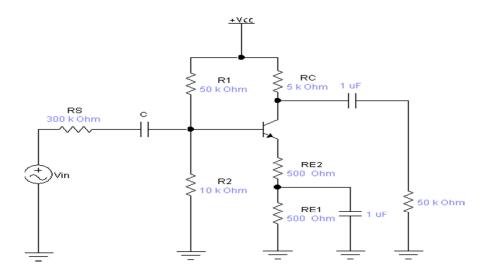

Given the amplifier circuit below determine the total output voltage (ac and dc). Vcc = 10V,  $\beta$ dc=150,  $\beta$  = 175 RS = 300 $\Omega$ , R1=50K $\Omega$ , R2 = 10K $\Omega$ , Rc = 5K $\Omega$ ,

RE1=RE2 =

$$500\Omega$$

, Load = $50K\Omega$

## 7.0 REFERENCES/FURTHER READING

Fitchen F.C; (1972). Transistor Circuit Analysis and Design. Second Edition Van Nostrand Reinhold Publishers.

Maddock R.J and Calcutt D.M (1994). Electronics: a Course for Engineers Second Edition. Longman Publishers.

Neamen D.A (1996). Electronics Circuit Analysis and Design.

McGraw-Hill Publishers.

#### UNIT 3 FIELD EFFECT TRANSISTORS

#### **CONTENTS**

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Junction Field Effect Transistors

- 3.2 FET Configurations

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Readings

#### 1.0 INTRODUCTION

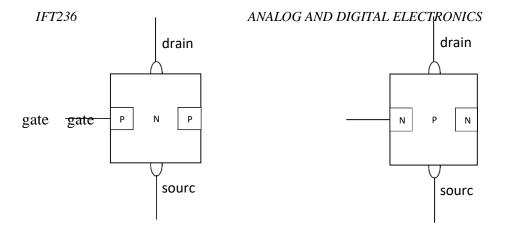

The concept upon which the field - effect transistor or FET is based is that the width of a conducting channel in a semiconductor may be varied by the external application of an electric field. Thus, FETs behave as voltage-controlled resistors. These devices can be grouped into three major categories. The first two categories are both types of metal-oxide-semiconductor field-effect transistors, or MOSFETs: enhancement-mode MOSFETs and depletion-mode MOSFETs. The third category consists of junction field-effect transistors, or JFETs. In addition, each of these devices can be fabricated either as an n-channel device or as a p-channel device, where the n or p designation indicates the nature of the doping in the semiconductor channel.

#### 2.0 OBJECTIVES

At the end of this unit, students are expected be able to:

- be able to IDENTIFY field effect transistor symbols

- be able to ANALYZE basic FET amplifier topologies for gains and resistances

- be able to DISCUSS the relative properties of various FET configurations

- be able to DESIGN basic amplifiers to meet or exceed stated specifications.

#### 3.0 MAIN CONTENT

Junction Field Effect Transistors

There are two general classes of FETs

The Metal Oxide Semiconductor FET (MOSFET)

The Junction FET (JFET)

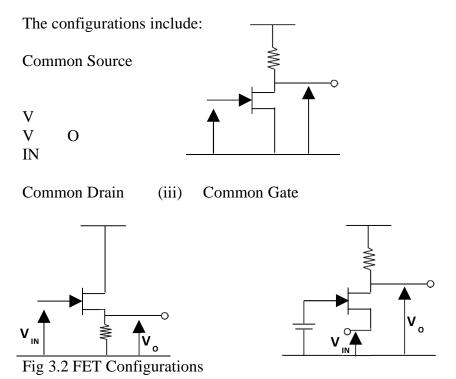

# **FET Configurations**

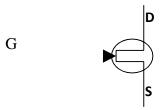

The FET is similar to the BJT transistor in terms of the number of terminals and configuration. The FET has three terminals as shown below.

Fig 3.1 FET symbol

The JFET is made up of a Semiconductor region known as the Channel with ohmic contacts at each end. The Channel material can either be N-type of P-type as shown below:

Fig 3.3 N channel JFET Fig 3.4 P channel JFET

The JFET is always operated with the Gate to Source voltage in Reverse Bias as shown below.

Fig 3.5 JFET Operation

In a P channel JFET, the P and N Junctions are reversed from those of the N Channel. In the P channel device, the Majority Carriers are holes (Positive Charges) and due to the low mobility of holes. The N-channel is often times preferred.

When VGS is increased, more positive ions are injected into the P side and this narrows the depletion region there by widening the channel and increasing the current flow. When VGS is decreased (made more negative), more positive ions are taken from the P side and the depletion region widens leading to a narrowing of the channel, reducing ID flow. When VGS becomes more negative to a point where ID=0, the conduction known as pinch-off arises.

Drain current at Pinch-Off is essentially zero. The PN JFET is a normally-On device and its current flow is controlled by the gate and can only be switched off by applying a suitable voltage to the gate terminal

For the JFET,

$$ID = IDSS \left[ 1 - \frac{VGS}{VGS(qff)} \right]$$

Where  $IDSS = maximum \ value \ of \ ID \ when \ VGS = 0 \ VGS(off) = value \ of \ VGS \ when \ FET \ will be \ off$

## Example 1

Given IDSS =

$$12mA$$

, VGS (off) =  $-5V$ , determine the value of ID at VGS =  $0$ ,  $-1$ ,  $-4$ .

Solution:

For

$$V_{GS} = 0$$

2 2

$ID = IDSS \left[ 1 - \frac{VGS}{VGS(off)} \right] = 12mA \left[ 1 - \frac{0}{-5V} \right]$

= 12mA  $[1 + 0]^2 = 12mA$

For

$$V_{GS} = -1$$

$$I_D = 12\text{mA} \left[ 1 - \frac{2}{\frac{1}{2}} \right]$$

= 12mA  $\left[ 1 - \frac{1}{5} \right] = 7.68\text{mA}$

For

$$V_{GS} = -4$$

$$I_D = 12\text{mA} \left[ 1 - \frac{2}{-5} \right]^2 = 12\text{mA} \left[ 1 - \frac{4}{5} \right]$$

= 0.48mA

For the N channel JFET,

- $VDD \square IDRD \square VD$

- $VD \square VDD \square$

- $VGS \square VG \square$

- **IDRD VS**

- $R \qquad V \qquad VGS \ \ \Box$

- $0 \square VS$

- $VS \square$

- **IDRS**

- $\square$  For N channel, the VGS = -IDRS For P channel, the VGS = IDRS

- $\mathsf{VDD} \; \Box \; \mathsf{IDRD} \; \Box \; \mathsf{VDS} \; \Box \; \mathsf{VS} \; \mathsf{VS} \; \Box \; \mathsf{IDRS}$

- $VDD \square$

- IDRD  $\square$  VDS  $\square$

- **IDRS**

- VDS

- $VDD\ \Box$

- ID(RD □

- RS)

## Example 2

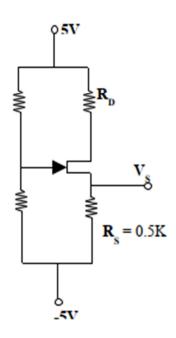

Given the circuit below with the following transistor parameters of IDSS = 5mA, Vp = VGS = -4V, design the circuit such that ID = 2mA, VDS = 6V

## Solution

$$ID = IDSS \left( 1 - \frac{VGS}{Vp} \right)$$

$$2 = 5 \left( 1 - \frac{VGS}{-4} \right)$$

$$\left( 1 - \frac{VGS}{-4} \right) = \frac{2}{5}$$

Take the square root of both sides

$$\sqrt{1 - \frac{V_{GS}}{-4}} = \sqrt{0.4}$$

$$1 - \frac{V_{GS}}{-4} = 0.63$$

$$- \frac{V_{GS}}{-4} = 0.63 - 1 = -0.37$$

$$- V_{GS} = (-4)(-0.37) = 1.48$$

$$- V_{GS} = 1.48V$$

$$\therefore V_{GS} = -1.48V$$

| From the diagram $IDRS = -VGS$                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VGS                                                                                                                                                                                 |

| $\square$ ID $\square$ RS $\overline{}$                                                                                                                                             |

|                                                                                                                                                                                     |

| $\square$ RS $\square$ ID $\square$                                                                                                                                                 |

| 1.48 🗆                                                                                                                                                                              |

| 2mA                                                                                                                                                                                 |

| 0.74K□                                                                                                                                                                              |

| From the output equation,                                                                                                                                                           |

| VDD □                                                                                                                                                                               |

| $IDRD \square VDS \square$                                                                                                                                                          |

| IDRS                                                                                                                                                                                |

| VDS □                                                                                                                                                                               |

| VDS □                                                                                                                                                                               |

| $VDD\;\square$                                                                                                                                                                      |

| 6V                                                                                                                                                                                  |

| ID $\square$                                                                                                                                                                        |

| IDRS                                                                                                                                                                                |

| $\square$ RD $\square$                                                                                                                                                              |

| $VDD \square VDS \square IDRS \square$                                                                                                                                              |

| ID                                                                                                                                                                                  |

| $10 \square 6 \square \square 2mA \square \square 0.74K \square$                                                                                                                    |

| 2mA                                                                                                                                                                                 |

| $RD\;\square$                                                                                                                                                                       |

| 4 □ 1 <u>.48 □</u>                                                                                                                                                                  |

| 2                                                                                                                                                                                   |

| 1.26K□                                                                                                                                                                              |

| Example 3 Given the circuit below, the transistor parameters are IDSS = $12\text{mA}$ , $Vp = -3.5V$ , $R1+R2 = 100K$ . Design the circuit such that $ID = 5\text{mA}$ , $VDS = 5V$ |

$$ID = IDSS \left( 1 - \frac{VGS}{Vp} \right)$$

$$5 = 12 \left( 1 - \frac{VGS}{Vp} \right)^2$$

$$\frac{5}{12} = \left( 1 - \frac{VGS}{-3.5} \right)$$

# Square root both sides

$$\sqrt{0.42} = \sqrt{1 - \frac{V_{GS}}{-3.5}}$$

$$0.65 = 1 - \frac{V_{GS}}{-3.52}$$

$$-\frac{V_{GS}}{-3.5} = -0.35$$

$$-V_{GS} = 1.24V$$

$$V$$

GS =  $-1.24V$

From the circuit,

VS  $\square$

IDRS □ 5 □

$\square$  5  $\square$   $\square$  0.5  $\square$   $\square$

5 □ □ 2.5V

VGS  $\square$

$VG \square VS \square VG \square$

$VGS \square VS$

VGS  $\square$   $\square$  1.24  $\square$   $\square$  2.5  $\square$   $\square$  1.24  $\square$  2.5  $\square$   $\square$  3.74V

From potential divider

VG □ R2 □ □ V □

$\overline{R1} \square \overline{R2}$

$\square$  3.74  $\square$  R2  $\square$  10  $\square$  5

100

$R2 \ \square \ 10 \square \ \square \ \square \ 3.74 \ \square \ 5 \ 100$

| R2 □                                                         |

|--------------------------------------------------------------|

| 10                                                           |

| R2 □                                                         |

| R1 □                                                         |

| 1.26K                                                        |

| 12.6K                                                        |

| 100K □                                                       |

| 12.6K □                                                      |

| 87.4K□                                                       |

| $VDD \square$                                                |

| $IDRD \square VDS \square$                                   |

| IDRS                                                         |

| $\square$ RD $\square$                                       |

| $VDD \square VDS \square IDRS \square$                       |

| ID                                                           |

| $10 \square 5 \square \square 5 \square \square 0.5 \square$ |

| 5                                                            |

| RD □                                                         |

| 10 □ 5 □                                                     |

| 5                                                            |

| 2.5 □                                                        |

| 0.5K□                                                        |

#### 4.0 CONCLUSION

In this unit you have been introduced to the Field effect transistor amplifier and the different types of biasing arrangements and FET configurations.

#### 5.0 SUMMARY

In this unit we have been able to extend knowledge of the theory and applications of transistors and transistor amplifier design.

## 6.0 TUTOR-MARKED ASSIGNMENT

Given IDSS = 12mA, VGS (off) = -4V, determine the value of ID at VGS = 0, -1, -4.

## 7.0 REFERENCES/FURTHER READING

Fitchen F.C; (1972). Transistor Circuit Analysis and Design. Second Edition Van Nostrand Reinhold Publishers.

Neamen D.A (1996). Electronics Circuit Analysis and Design.

McGraw-Hill Publishers.

#### **MODULE 2**

Unit 1 Introduction to Feedback

Unit 2 Operational Amplifiers (OPAMPS)

#### UNIT 1 INTRODUCTION TO FEEDBACK

#### **CONTENTS**

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Feedback Amplifiers

- 3.2 Types of Feedback Arrangements

- 3.3 Effect of Negative Feedback on Amplifiers

- 3.4 Types of Negative Feed back Topologies

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Readings

#### 1.0 INTRODUCTION

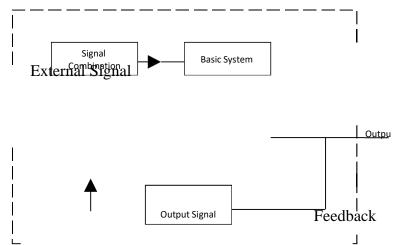

A feedback system is a system in which the input signal is modified by the system output before the internal processing by the system itself. The block diagram in a typical feedback system is shown in figure 4.1 below.

Figure 4.1: Typical Feedback system

The signal combination is usually a simple addition or subtraction. Multiplication, logical or other combination can also be used. The output signal processing is often a simple attenuation or amplitude reduction.

#### 2.0 OBJECTIVES

At the end of this unit, students should be able to:

- be able to IDENTIFY feedback amplifier topologies

- be able to ANALYZE feedback amplifier topologies

- be able to DISCUSS the relative benefits and possible drawbacks of feedback amplifier topologies with respect to basic amplifier topologies

- be able to APPLY the concepts of feedback analysis to the DESIGN of analog amplifiers to meet or exceed stated specifications.

## 3.0 MAIN CONTENT

Feedback Amplifiers

A feedback amplifier consists of two parts

The Amplifier system The feedback system

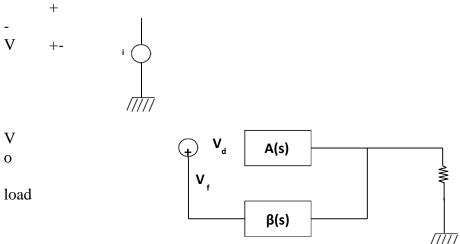

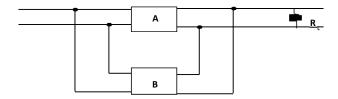

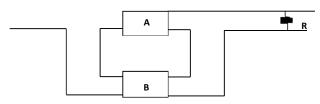

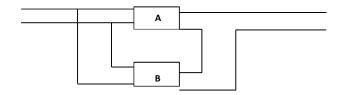

The classic block diagram for a feedback system is given in figure 4.2 below.

Figure 4.2: Classic feedback block system

The amplifier A(s) when used without the feedback is said to be in open loop with the gain denoted by A01.

From the circuit in figure 4.2 above.

| $Vd \square Vi \square Vf Vo \square A01Vd$                                       |

|-----------------------------------------------------------------------------------|

| (1)                                                                               |

| (2)                                                                               |

| $Vf \square \square Vo$                                                           |

| (3)                                                                               |

| From equation (2), substitute for Vd                                              |

| Vo □ A01□Vi □ Vf □ But Vf □ □ Vo                                                  |

| $Vo = A01(Vi - \beta Vo)$ (4)                                                     |

| Expand (4) and collect like terms                                                 |

| $Vo = A01Vi - A01\beta Vo$                                                        |

| $A01Vi = Vo + A01\beta Vo = Vo(1 + A\beta) $ (5)                                  |

| $A01Vi = Vo(1 + A01\beta)$                                                        |

| $\therefore \frac{Vo}{Vi} = \frac{A01}{1 + A01\beta} = ACL $ (6)                  |

| The Voltage The Voltage gain for the closed loop is given to be ACL □ Vo □ Vi A01 |

| $\overline{1 \square A01}\square$                                                 |

| A01 = open loop gain                                                              |

| $\beta = feedback$ attenuation factor $A01\beta = loop\ gain = T$ ACL $\Box$ A01  |

| $\overline{1 \Box T}$                                                             |

Types of Feedback Arrangements

There are two basic types of feedback arrangements and these are:

#### Positive Feedback

In the positive feedback arrangement, the feedback voltage is in the same phase as the input voltage and it increases the input voltage amplitude. It leads to instability in systems and is only used in oscillator design.

For Positive Feedback (PFB)  $Vd \square Vi \square Vf$ Vo □ A01Vd Vo □  $A01 \square Vi \square Vf \square \square$  $A01 \square Vi \square \square Vo \square$ Vo □ A01Vi □ A01□ Vo A01Vi □ Vo □A01□ Vo □ Vo□1 □  $A \sqcap \sqcap$ Vo  $\Box$  1  $\Box$  A01 Vi A01 □  $\square$  ACL  $\square$ Vo □ Vi A01 1 □ A01 □ **PFB** Negative Feedback

In negative feedback, the feedback voltage is 1800 out of phase with the input voltage. This leads to a reduction in the input voltage and this stabilizes the system. It is used mostly in amplifier.

Negative Feedback (NFB)

$$Vd = Vi - Vf$$

$$Vo = A01Vd$$

$$Vo = A01(Vi - \beta Vo) = A01Vi - A01\beta Vo$$

$$A01Vi = Vo + A01\beta Vo = Vo(1 + A01\beta)$$

$$\frac{Vi}{Vo} = \frac{1 + A01\beta}{A01}$$

$$\therefore ACL = \frac{Vo}{Vi} = \frac{A01}{1 + A01\beta}$$

NFB

Both gain A and feedback  $\beta$  may be complex quantities having both a modulus and an angle which may depend on signal frequency.

For NFB, T = Positive > 0 For PFB, T = Negative < 0

### SELF ASSESSMENT EXERCISE

The gain and feedback factor of an amplifier at different frequencies are listed below. For each case, determine the nature of the feedback and system gain.

F1 F2 F3 F4 A 5000<180° 4500<160° 1000<65° 500<20°

$$β$$

0.02<0° 0.018<-5° 1.148 x 10-3<-10° 0,001<-15°  $\frac{F1}{2}$  ACL  $\frac{1}{2}$  500 180 180 5000  $\frac{1}{2}$  180 101 180 49.5  $\frac{1}{2}$  1800

Solve the rest.

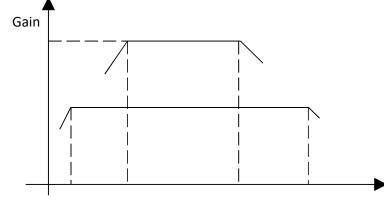

| From our previous discussion, the gain of an amplifier (Voltage gain) without feedback is higher than the gain with negative feedback while it is lower than the gain of the amplifier with positive feedback. $AV(NFB) < AV < AV(PFB).$              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Effect of Negative Feedback on Amplifiers                                                                                                                                                                                                             |

| Gain and Gain Stability                                                                                                                                                                                                                               |

| Typical amplifiers are subject to changes such as temperature, dc supply levels and ageing. Such change results in variation in amplifier gain. Negative feedback helps to reduce the variation in gain to acceptable limits (or stabilize the gain). |

| For a NFB amplifier                                                                                                                                                                                                                                   |

| ACL □<br>A01                                                                                                                                                                                                                                          |

| $ \overline{1 \square A01} \square $ $ A01\beta >> 1 $ $ ACL \square $ $ A01 \square 1 $                                                                                                                                                              |

| $\overline{A01}$ $\Box$                                                                                                                                                                                                                               |

| The feed back ration $\beta$ is often determined by the ratio of two resistors.                                                                                                                                                                       |

| Example 1 The gain of an amplifier is found to be 750 on test but under conditions of reduced dc supply and external loading, the value reduced to 400.                                                                                               |

The gain of an amplifier is found to be 750 on test but under conditions of reduced dc supply and external loading, the value reduced to 400. Compare this percentage variation for the amplifier with the corresponding variation if NFB of (a) 0.005 (b) 0.03 (c) 0.1 is used.

## Solution

| Doracion     |         |           |         |             |                |             |

|--------------|---------|-----------|---------|-------------|----------------|-------------|

| Percentage v | variati | on of ga  | in with | out feed ba | ck is original | □ new □ 100 |

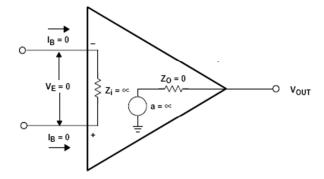

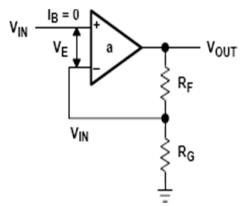

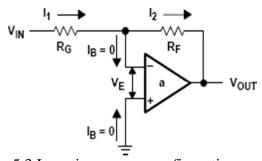

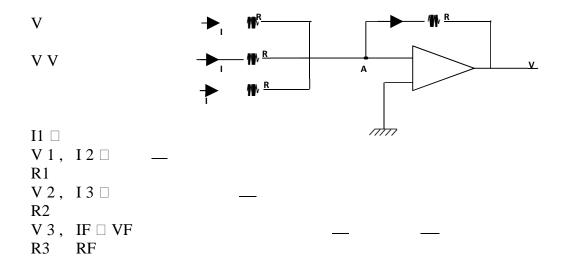

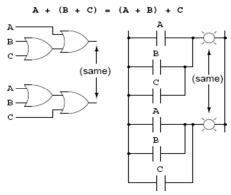

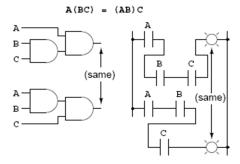

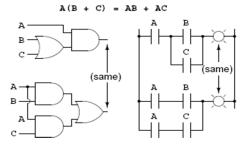

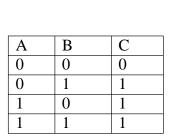

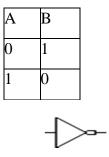

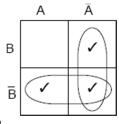

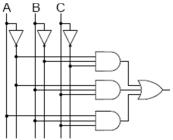

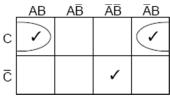

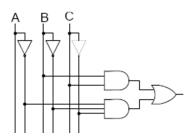

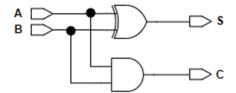

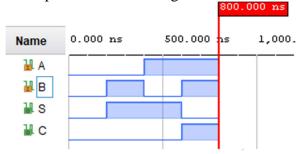

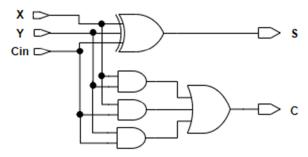

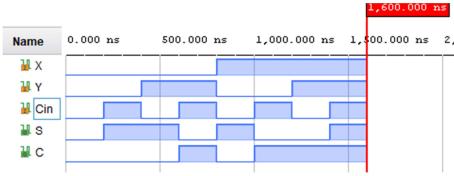

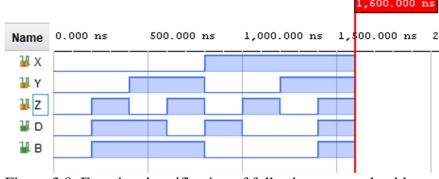

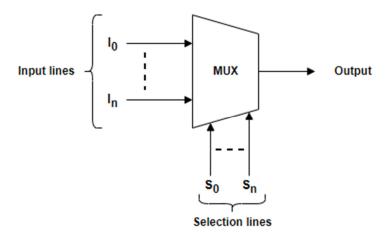

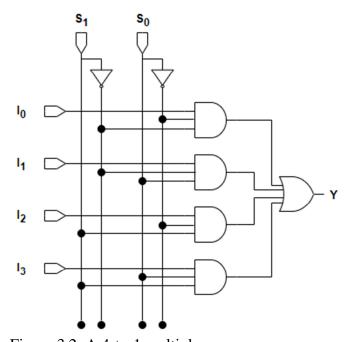

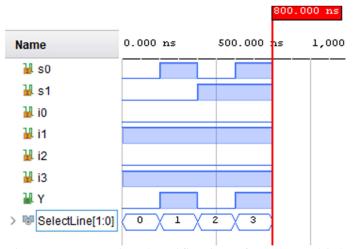

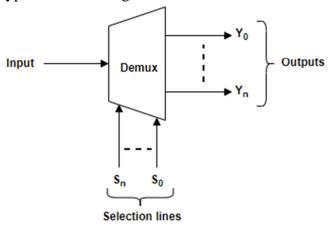

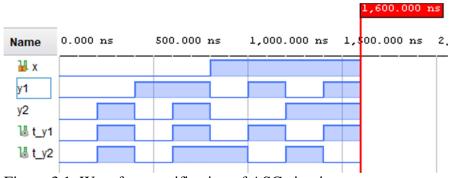

| □ 750 □ 40   | 0 🗆 1   | $\square$ |         |             |                |             |